## Three Phase sinusoidal BLDC Motor controller

### **Description**

The FT1007S is a Three Phase sinusoidal Brushless DC (BLDC) Motor controller with built-in driver. It comes with Hall insensitive sensor design providing both SVPWM and BLDC drive with constant/variable lead angle. Open/Closed loop speed adjustment can be achieved through either direct-PWM or analog voltage, initiated by soft-start. Speed indicator is provided through a Frequency Generator output, generating digital pulse with a configurable frequency proportional to the speed of the motor.

Protection functions of FT1007S are comprehensive including lock protection and automatic recovery, thermal shutdown, current limit and over current protections. These prevent the control circuits and the motor from being damaged, particularly under stressed applications and demanding environments.

#### **Feature**

- Selectable SVPWM (sine-wave) or BLDC (120°) drives

- Hall sensor/ Hall IC input supported

- 180° sinusoidal drive, for high efficiency and low acoustic noise

- Precharging feature

- Intelligent Soft-start

- Constant/Variable lead angle control

- Open/Closed loop speed adjustment can be selected (direct-PWM and analog voltage control).

- FG (Frequency Generator)

- Current limit and over current protection

- Built-in lock protection and automatic recovery circuit

- Built-in thermal shutdown protection (TSD)

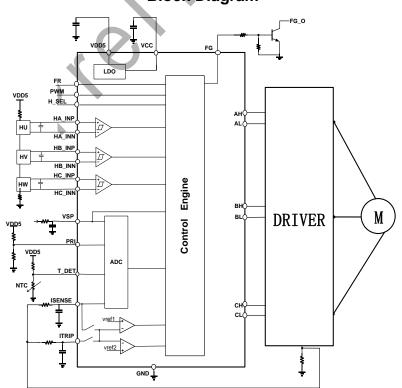

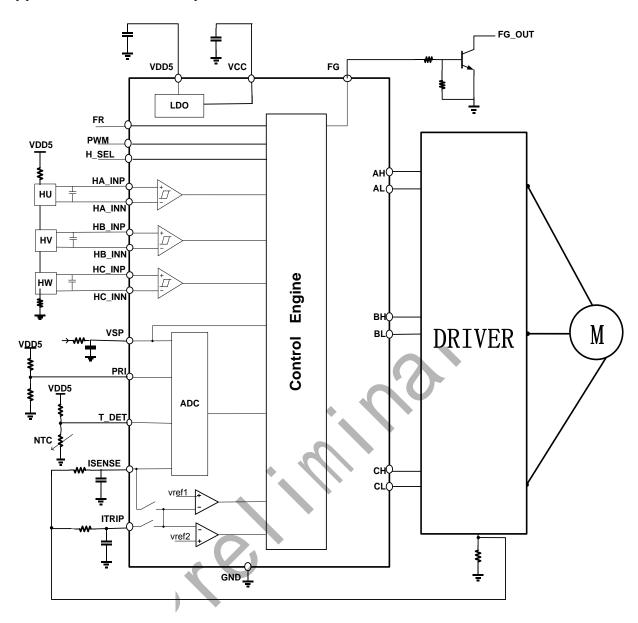

### **Block Diagram**

REV\_ Preliminary 2 www.fortiortech.com

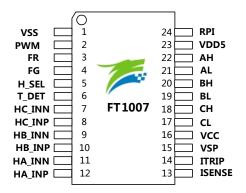

## **Pin Assignment**

## SSOP24

# Pin Configuration

| PIN NO. | PIN Name | Type  | Description                                                  |  |  |

|---------|----------|-------|--------------------------------------------------------------|--|--|

| 1       | VSS      | GND   | Signal and power ground.                                     |  |  |

| 2       | PWM      | Ι     | Digital speed control (Floated when using VSP speed control) |  |  |

| 3       | FR       | I     | Motor rotation direction input                               |  |  |

| 4       | FG       | 0     | Open drain. Frequency Generator, speed signal output         |  |  |

| 5       | H_SEL    | Ι     | Hall type selection                                          |  |  |

| 6       | T_DET    | Ι     | Thermal detection input                                      |  |  |

| 7       | HC_INN   | Ι     | Hall C - Sensor Input. Phase-W magnetic field detection      |  |  |

| 8       | HC_INP   | Ι     | Hall C + Sensor Input. Phase-W magnetic field detection      |  |  |

| 9       | HB_INN   | Ι     | Hall B - Sensor Input. Phase-V magnetic field detection      |  |  |

| 10      | HB_INP   | Ι     | Hall B + Sensor Input. Phase-V magnetic field detection      |  |  |

| 11      | HA_INN   | I     | Hall A - Sensor Input. Phase-U magnetic field detection      |  |  |

| 12      | HA_INP   | I     | Hall A + Sensor Input. Phase-U magnetic field detection      |  |  |

| 13      | ISENSE   | I     | Current limit & Lead angle analog input                      |  |  |

| 14      | ITRIP    | Ĭ     | Current sensor voltage feedback analog input                 |  |  |

| 15      | VSP      | Ι     | Speed control                                                |  |  |

| 16      | VCC      | POWER | Power supply                                                 |  |  |

| 17      | CL       | Ι     | PWM output of phase W. Low side                              |  |  |

| 18      | СН       | Ι     | PWM output of phase W. High side                             |  |  |

| 19      | BL       | Ι     | PWM output of phase V. Low side                              |  |  |

| 20      | ВН       | Ι     | PWM output of phase V. High side                             |  |  |

| 21      | AL       | I     | PWM output of phase U. Low side                              |  |  |

| 22      | АН       | I     | PWM output of phase U. High side                             |  |  |

| 23      | VDD5     | 0     | Digital power output, LDO DC5V output for digital signal     |  |  |

| 24      | RPI      | I     | Soft start duty setting                                      |  |  |

**REV\_ Preliminary** 3 www.fortiortech.com

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may be damaged or may not function or be operational above these ratings and stressing the device to/above these levels is not recommended. Fortior does not recommend exceeding or designing about the Absolute Maximum Ratings.

| Parameter                       | Symbol               | Condition | Ratings  | Unit         |

|---------------------------------|----------------------|-----------|----------|--------------|

| Power supply voltage            | V <sub>cc</sub> max  |           | 30.0     | V            |

| FG output current               | I <sub>FG</sub> max  |           | 10       | mA           |

| FG output pin withstand voltage | V <sub>FG</sub> max  |           | 5.5      | V            |

| VSP pin withstand voltage       | V <sub>VSP</sub> max |           | 20       | V            |

| Operating temperature           | Topr                 |           | -40~+125 | $^{\circ}$ C |

| Storage temperature             | Tstg                 |           | -65~+150 | $^{\circ}$   |

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications.

| Symbol               | Parameter Min.      | Тур. | Max. | Unit |

|----------------------|---------------------|------|------|------|

| Power supply voltage | V <sub>cc</sub> 3.7 | 12   | 18   | V    |

**REV\_ Preliminary** 4 www.fortiortech.com

### **Electrical Characteristics**

For guaranteed specifications and test conditions, consult the Electrical Characteristics.

Unless otherwise specified, Ta=25  $^{\circ}$ C , VCC=12V

| Devemates                                        | Symbol             | Condition                | Ratings |      |       | Unit       |

|--------------------------------------------------|--------------------|--------------------------|---------|------|-------|------------|

| Parameter                                        |                    |                          | Min.    | Тур. | Max.  | Onit       |

| Power supply current                             | I <sub>cc</sub>    | Working                  |         | 10   | 15    | mA         |

| VDD5 LDO                                         |                    |                          |         |      |       |            |

| Regulator voltage                                | VDD5               |                          | 4.9     | 5    | 5.1   | V          |

| Regulator output current                         | lv5out             | VDD5=5V                  |         |      | 10    | mA         |

| Analog I/O Section*Note1                         |                    |                          |         |      |       |            |

| Analog Input range                               |                    |                          | 0       |      | 5.3   | V          |

| Digital Input Section*Note2                      |                    |                          |         |      |       |            |

| High-level input voltage                         | Vdinh              |                          | 2.5     |      | 5.3   | V          |

| Low-level input voltage                          | Vdinl              |                          | 0       |      | 2.0   | V          |

| Output Section *Note3                            |                    |                          |         |      |       | •          |

| High-level output voltage                        | Vdoh               | I <sub>o</sub> =5mA      | 4.5     |      | 5.0   | V          |

| Low-level output voltage                         | Vdol               | I <sub>o</sub> =-5mA     | 0       |      | 0.7   | V          |

| Dead time                                        | T <sub>DT</sub>    |                          |         | 2    |       | us         |

| FG Output Pin                                    |                    | ~0                       |         |      |       | •          |

| FG output pin low-level voltage                  | VFG                | When I <sub>o</sub> =5mA | -       | 0.1  | 0.2   | V          |

| Hall Input Pin*Note4                             |                    |                          |         |      |       |            |

| Hall sensor input sensitivity                    | VHN                | Hysteresis               |         | 10   | 20    | mV         |

| <b>*</b>                                         | VIIIV              | voltage                  |         | 10   | 20    | IIIV       |

| External PWM Input                               |                    |                          |         |      |       |            |

| External PWM input frequency                     | F <sub>PWMIN</sub> |                          | 1       |      | 50    | kHz        |

| Thermal Protection Circuit                       |                    |                          |         |      |       |            |

| Thermal protection circuit operating temperature | TSD                |                          |         | 150  |       | $^{\circ}$ |

| Temperature hysteresis width                     | △TSD               |                          |         | 30   |       | $^{\circ}$ |

| Low-Voltage Detection                            |                    |                          |         |      |       |            |

| Low voltage detection voltage                    | UVLO               |                          |         | 3.0  |       | V          |

| ADC *Note5                                       |                    |                          |         |      |       |            |

| Input range                                      |                    |                          | 0       |      | VDD5  | V          |

| INL                                              | INL                |                          |         | 0.1  | 0.125 | LSB        |

| DNL                                              | DNL                |                          |         | 0.2  | 0.5   | LSB        |

- 1. Note1:ISENSE、ITRIP、T\_DET.

- 2. Note2:FR、PWM.

- 3. Note3:AH、AL、BH、BL、CH、CL

- 4.Note4: HA\_INN、HA\_INP、HB\_INN、HB\_INP、HC\_INN、HC\_INP

- 4.Note5:VSP、T\_DET、RPI

**REV\_ Preliminary** 5 www.fortiortech.com

### **Functional Description and Notes**

Please read the following notes before designing driver circuits with FT1007S.

#### 1. Setting of Function

Many functions can be set by programming efuses within the chip. These functions include: selection of SVPWM (sine-wave) or BLDC ( $120^{\circ}$ ) modulation mode, selection of current protection, selection of open loop speed control or close loop speed control, etc.

### 2. Differential Hall Signal

$HA_INN \setminus HA_INP \setminus HB_INN \setminus HB_INP \setminus HC_INN \setminus HC_INP$  are the differential Hall sensor inputs from the assembled motor and must be proportionately stepped down to less than VDD5 for IC protection.  $HA_INP \setminus HB_INP \setminus HC_INP$  are the Hall IC inputs from the assembled motor, if Hall ICs are used.  $HA_INN \setminus HC_INN$  is to be connected to ground for HALL IC applications.

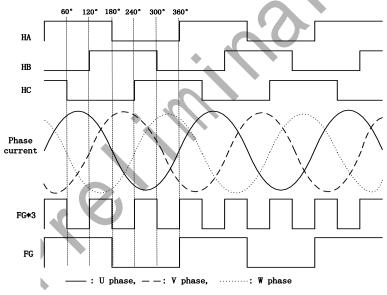

#### 3. SVPWM Mode and BLDC Mode

FT1007S can run in SVPWM mode for motor control. Under SVPWM mode, the phase currents are sinusoidal for acoustic noise reduction. The corresponding sequence diagram is shown in Figure 1.

Figure 1 Sequence diagram for 3 Hall

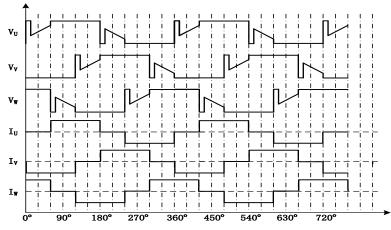

FT1007S can also be programmed to drive the motor with the traditional BLDC ( $120^{\circ}$ ) mode. The voltage and current sequence diagram is shown in Figure 2.

**REV\_ Preliminary** 6 www.fortiortech.com

Figure 2 Voltage and Current of BLDC(120°)

### 4. Speed Control Methods

FT1007S has two methods to control speed, through direct digital PWM input or analog voltage input. If digital PWM input is used, PWM input duty direct input to control speed. If analog voltage speed control is used, the voltage seen at SPEED will generate an internal PWM with its duty cycle determined by the following equation:

$$Duty\_cycle = \frac{VSP - 2.1}{3.3}$$

VSP speed control is used, PWM pin needs to be floated. The selection of digital PWM input control or analog voltage is done through efuse.

#### 5. Closed loop speed control

Closed loop speed control can be is controlled through the duty cycle of the digital input PWM or the voltage level of the analog input PWM. Additional efuses (VLOW and VRANGE) together with SMIN\_DUTY can be set in order to achieve the speed profiles. This is achieved using an internal PI loop with its proportional and integral gains configurable through efuses.

#### 6. Frequency Generator

The Frequency Generator output generates a rotation pulse providing information about the speed of motor. It can be programmed using internal efuse to give 2 mechanical rotations for motor pole pairs ranging from 2-8, or 1-3 per electrical rotation. The default setting is 1 pulse per electrical degree. The FG pin is an open drain output, which is to be connected to a logical voltage level through an external pull-up resistor when used. This pin can be left open if unused.

#### 7. Intelligent Soft-start

FT1007S can be started with soft-start as configured by efuse. Under open loop PWM control, the motor is started with initial starting PWM duty and subsequently increased/reduced to the input PWM duty cycle after a configurable number of soft start cycles. However, in the event of rotation at start, to avoid VCC overshoot, FT1007S will bypass the initial starting PWM duty stage and connect the input PWM straight to the output. Under closed loop, the soft start cycle must not be zero.

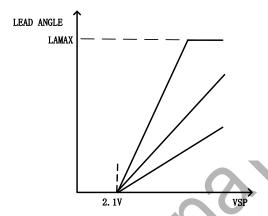

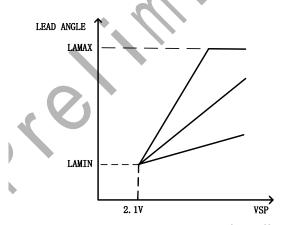

#### 8. Lead Angle

The lead angle of generated motor driving signals relative to the Hall signals can be shifted by an angle between 0 and 63 degrees. The lead angle controlled by VSP pin. For lead angle control, The user can set min lead angle  $(LA_{MIN})$ , max lead angle  $(LA_{MAX})$  and lead angle skew  $(LA_{SKEW})$  for their application. Min lead angle  $(LA_{MIN})$ , max lead

**REV\_ Preliminary** 7 www.fortiortech.com

angle  $(LA_{MAX})$  and lead angle skew  $(LA_{SKEW})$  can be programmed by setting internal efuse and the final lead angle (LA) is determined by the equation:

$$LA = LA_{MIN} + LA_{SKEW} * (VSP - 2.1)$$

\*note: LA<63;

LA<sub>MIN</sub>: min lead angle, it can be set from 0° to +63° at 1° intervals, internal efuse setting;

LA<sub>SKEW:</sub> lead angle skew,

$LA_{SKEW} = 64/(64-n);$

here 'n' is internal efuse setting, it can be set from 0 to 63 at 1 intervals,;

LA<sub>MAX</sub>: max lead angle, it can be set from 0° to +63° at 1° intervals, internal efuse setting;

Figure 3. Phase Control Setting Example 1, LA<sub>MIN</sub>=0; difference LA<sub>SKEW</sub>

Figure 4. Phase Control Setting Example 2, LA<sub>MIN</sub>≠0; Difference LA<sub>SKEW</sub>

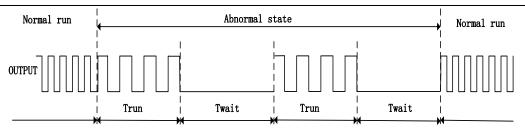

### 9. Lockup Protection and Automatic Restart

If motor rotation is abnormal, and the motor stalls for a duration of Trun, the lock-up protection circuit will disable the driver (by setting its outputs to high-impedance) in order to prevent the motor coil from burnout. After a "waiting time (Twait)", lock-up protection is released and normal operation will be resumed. Similarly, if rotation is abnormal for another time period, Trun, lock-up protection is triggered. Twait and Trun timings are configurable with internal efuses and can be modified by user. The number of restarts after stall detection can also be configured to 1, 3, 8 or infinite times depending on efuse setting.

**REV\_ Preliminary** 8 www.fortiortech.com

Figure 5 Lockup Protection and Automatic Restart

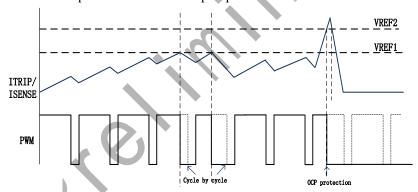

#### 10. Current Protection

There are three methods of current protection: overload current limit protection, cycle by cycle current limit protection (only available for BLDC) and over current protection. The overload current limit protection and cycle by cycle current limit protection of the motor can be selected by setting internal efuse

The current limit circuit limits the output current peak value to a level determined by the equation:

$$I = Vref 1 / R_{ISENSE}$$

For the overload current protection mode, the current limit circuit detects the peak current of the output transistors at the ISENSE pin and then reduces the duty cycle of PWM.

For the cycle by cycle current protection mode, when the voltage at the ISENSE input is higher than Vref1, the current limit protection is generated and the output PWM is turned off and evaluated every PWM cycle.

For over current protection, when the voltage at the Itrip input is higher than vref2, the over current protection will be triggered, and outputs are immediately turned off. After a "waiting time" (Twait), the over current protection will be released and FT1007S restarts its operation with the startup sequence.

Figure 6 Cycle by cycle current limit protection mode and over current protection

Vref1:Internal Reference voltage1,the vref1 voltage can be set to 0.3V \ 0.4V \ 0.5V or 0.6V by setting internal efuse. Vref2: Internal Reference voltage2, typically 1.0V.

#### 11. Thermal Protection.

FT1007S has a built in thermal shut down function, which will shut down the device when the junction temperature is over  $150 \, \text{C}$  and will resume operating when the junction temperature drops back to  $120 \, \text{C}$ .

#### 12. Thermal Control

FT1007S has a thermal control input Pin: T\_DET. Through this input, the pwm duty cycle of the output can be controlled whenever thermal operating conditions has been exceeded.

**REV\_ Preliminary** 9 www.fortiortech.com

Figure 7 thermal control circuit

T\_DET can be connected to a NTC as illustrated in the figure. When the temperature increases, the resistance of the NTC will reduce, pulling down the voltage at T\_DET. If the voltage goes below 2.15V, the output pwm duty cycle will slowly reduce. Duty cycle reduction will continue until it reaches minimum duty cycle (e.g. 4.5%) or when the voltage at T\_DET goes above 2.15V. The voltage at T\_DET rises as the duty cycle reduction causes a reduction in motor speed and temperature. This reduction in temperature will increase the resistance of the NTC and the voltage at T\_DET. If the voltage at T\_DET exceeds 2.15V, the output pwm duty cycle will increase. Duty cycle increase will continue until it reaches the input pwm duty cycle or when the voltage at T\_DET goes below 2.15V.

#### 12. Precharging

FT1007S can be started with precharging as configured through efuse. This is to charge the bootstrap capacitor during starting by providing a train of PWM duty 20% excitation of 40ms in each phase.

REV\_ Preliminary 10 www.fortiortech.com

## **Application Circuit Example**

REV\_ Preliminary 11 www.fortiortech.com

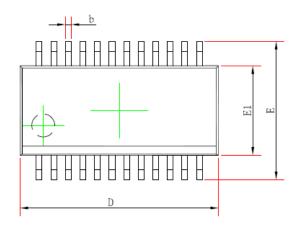

## **Package Information**

SSOP24

| Symbol | Dimensions In | Millimeters | Dimensions In Inches |        |  |

|--------|---------------|-------------|----------------------|--------|--|

|        | Min           | Max         | Min                  | Max    |  |

| A      |               | 1. 750      |                      | 0.069  |  |

| A1     | 0.100         | 0. 250      | 0.004                | 0.010  |  |

| A2     | 1. 250        |             | 0.049                |        |  |

| b      | 0. 203        | 0.305       | 0.008                | 0.012  |  |

| С      | 0.102         | 0.254       | 0.004                | 0.010  |  |

| D      | 8. 450        | 8.850       | 0. 333               | 0.348  |  |

| E1     | 3.800         | 4.000       | 0. 150               | 0. 157 |  |

| Е      | 5.800         | 6. 200      | 0. 228               | 0.244  |  |

| e      | 0.635 (BSC)   |             | 0. 025 (BSC)         |        |  |

| L      | 0.400         | 1.270       | 0.016                | 0.050  |  |

| θ      | 0°            | 8°          | 0 °                  | 8°     |  |

| Part Number | Package Type | Marking ID | Package Method | Quantity |

|-------------|--------------|------------|----------------|----------|

| FT1007S     | SSOP24       | FT1007S    | TUBE           | 58       |

REV\_ Preliminary 12 www.fortiortech.com

## **Copyright Notice**

Copyright by Fortior Technology (Shenzhen) Co., Ltd. All Rights Reserved.

Right to make changes —Fortior Technology (Shenzhen) Co., Ltd reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. The information contained in this manual is provided for the general use by our customers. Our customers should be aware that the personal computer field is the subject of many patents. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. It is the policy of Fortior Technology (Shenzhen) Co., Ltd. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

This manual is copyrighted by Fortior Technology (Shenzhen) Co., Ltd. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the expressly written permission from Fortior Technology (Shenzhen) Co., Ltd.

## Fortior Technology (Shenzhen) Co.,Ltd.

Room203, 2/F, Building No.11, Keji Central Road2, Software Park, High-Tech Industrial Park, Shenzhen, P.R. China 518057

Tel: 0755-26867710 Fax: 0755-26867715

URL: http://www.fortiortech.com

#### **Contained herein**

Copyright by Fortior Technology (Shenzhen) Co.,Ltd all rights reserved.