## FS236BQ

# Half-Bridge IPM

#### **Description**

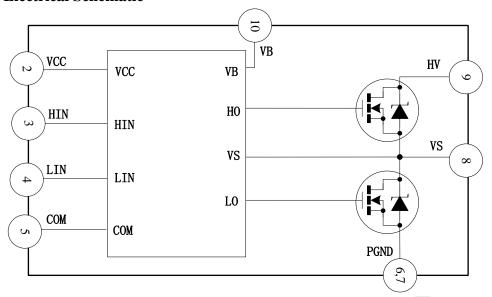

FS236BQ is a half-bridge module with high performance and high reliability, using for small power motor applications such as fan motor and bump, consisting of built-in 2 fast recovery MOSFET and half-bridge HVIC for gate driving.

FS236BQ has built-in VCC and VB under-voltage (UVLO) protection to prevent the power semiconductor devices from operation under very low voltage. The FS236BQ has also built-in cross-conduction and input signal filtering to prevent input noise.

FS236BQ is compact and suitable for built-in motors or any other applications requiring the compact installation.

#### **Features**

- Built-in 600V3A fast recovery MOSFET

- Built-in high voltage Gate driver circuit(HVIC)

- Power supply pressure range: 13.5V ~20V

- 3.3V/5V logic input compatible, active high HIN and LIN

- Under-voltage lockout for all channels

- Optimized dV/dt for loss and EMI trade offs

- Cross-conduction prevention logic

- Isolation 1500V<sub>RMS</sub> min

- ROHS compliant

#### Package(QFN10L-5\*6)

QFN10L-5\*6

### **Internal Electrical Schematic**

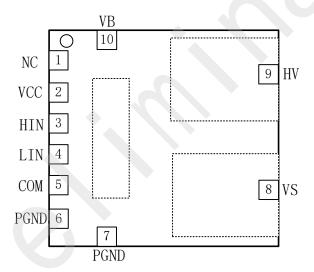

## **Module Pin-Out Description**

| Pin | Name | Description                             |  |

|-----|------|-----------------------------------------|--|

| 1   | NC   | Not Connect                             |  |

| 2   | VCC  | Low side and logic fixed supply         |  |

| 3   | HIN  | Logic Input for High Side (Active High) |  |

| 4   | LIN  | Logic Input for Low Side (Active High)  |  |

| 5   | COM  | Low Side Gate Drive Return              |  |

| 6,7 | PGND | Low Side Source Connection              |  |

| 8   | VS   | Phase Output                            |  |

| 9   | HV   | DC Bus                                  |  |

| 10  | VB   | High Side Floating Supply               |  |

REV\_Preliminary\_0.4 2 www.fortiortech.com

#### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the module may occur. These are not tested at manufacturing. All voltage parameters are absolute voltages referenced to VSS unless otherwise stated in the table. The thermal resistance and power dissipation ratings are measured under board mounted and still air condition.

| Symbol            | Description                                       | Min                 | Max                   | Unit |

|-------------------|---------------------------------------------------|---------------------|-----------------------|------|

| BV <sub>DSS</sub> | MOSFET Blocking Voltage                           | -                   | 600                   | V    |

| I <sub>O 25</sub> | DC output current per MOSFET @ TC=25°C (Note1)    | -                   | 3                     | A    |

| $I_{O~80}$        | DC output current per MOSFET @ TC=80°C (Note2)    | -                   | 2.1                   | A    |

| $I_{OP}$          | Peak output current per MOSFET @ TC=25°C          | -                   | 8                     | A    |

| Pd                | Power dissipation per MOSFET @ TC =25°C           | -                   | 3.57                  | W    |

| T <sub>J</sub>    | Maximum Operating Junction Temperature            | -                   | 150                   | °C   |

| $T_{\rm L}$       | Lead temperature (soldering 30 seconds)           | -                   | 260                   | °C   |

| $T_{S}$           | Storage Temperature Range                         | -40                 | 150                   | °C   |

| $R_{thJA}$        | Thermal resistance, junction to case, each MOSFET | -                   | 35                    | °C/W |

| $V_{B}$           | High side floating supply voltage                 | -0.3                | $V_{S} + 20 V$        | V    |

| $V_{S}$           | High side floating supply offset voltage          | V <sub>B</sub> - 20 | V <sub>B</sub> +0.3 V | V    |

| VCC               | Low Side fixed supply voltage                     | -0.3                | 20                    | V    |

| V <sub>IN</sub>   | Logic input voltage LIN, HIN                      | -0.3                | V <sub>CC</sub> +0.3  | V    |

| $V_{\rm ISO}$     | Isolation voltage(1min)(Note2)                    | -                   | 1500                  | V    |

**Note1:** The current is calculated based on the maximum junction temperature. Package limit is 1.1A.

Note2: The current is calculated based on the maximum junction temperature. Package limit is 0.8A.

Note3: In any case, power dissipation should not exceed P<sub>D</sub>.

Note4: Voltages above the absolute maximum ratings may damage the chip.

#### **Recommended Operating Conditions**

| Symbol            | Description                            | Min  | Тур | Max  | Units |

|-------------------|----------------------------------------|------|-----|------|-------|

| HV                | Positive DC Bus Input Voltage          |      | 300 | 400  | V     |

| $V_{BS}$          | High Side Supply Voltage               | 13.5 | 15  | 16.5 | V     |

| $V_{CC}$          | Low Side and Logic Supply Voltage      | 13.5 | 15  | 16.5 | V     |

| $V_{IN}$          | Logic Input Voltage                    | COM  |     | VCC  | V     |

| t <sub>dead</sub> | Blanking Time for Preventing Arm-Short | 1.0  |     |      | us    |

| $f_{PWM}$         | PWM Carrier Frequency                  |      | 15  | 20   | kHz   |

For proper operation, the module should be used within the recommended conditions. All voltages are absolute referenced to COM.

**Note1:** The long-term operation of the chip outside the recommended conditions may affect its reliability. It is not recommended to work in an environment that exceeds the recommended conditions.

REV\_Preliminary\_0.4 3 www.fortiortech.com

## Static Electrical Characteristics (V<sub>BIAS</sub> (V<sub>CC</sub>, V<sub>BS</sub>)=15V, T<sub>J</sub>=25°C, unless otherwise specified.)

| Symbol               | Description                                           | Min  | Тур  | Max  | Units | Conditions                |

|----------------------|-------------------------------------------------------|------|------|------|-------|---------------------------|

| BV <sub>DSS</sub>    | Drain-to-Source Breakdown Voltage                     | 600  |      |      | V     | I <sub>LK</sub> =1mA      |

| $I_{LK}$             | Zero Gate Voltage Drain Current                       |      |      | 250  | uA    | V <sub>DS</sub> =600V     |

| R <sub>DS(ON)</sub>  | Drain to Source ON Resistance                         |      | 2.4  | 3.0  | Ω     | $I_d = 1.5A$              |

| $V_{SD}$             | Diode Forward Voltage                                 |      |      | 1.2  | V     | $I_d = 1.5A$              |

| V <sub>IH</sub>      | Logic "1" input voltage for HIN/LIN                   | 2.8  |      |      | V     |                           |

| $V_{\rm IL}$         | Logic "0" input voltage for HIN/LIN                   |      |      | 0.8  | V     |                           |

| V <sub>CCUV+</sub>   | VCC Supply Under-Voltage, Positive Going Threshold    | 11.2 | 12   | 12.8 | V     |                           |

| V <sub>CCUV</sub> -  | VCC supply Under-Voltage,<br>Negative Going Threshold | 10.2 | 11   | 11.8 | V     |                           |

| V <sub>CCUVH</sub>   | VCC Supply Under-Voltage Lock- Out<br>Hysteresis      | 0.6  | 1    | -    | V     |                           |

| $V_{\rm BSUV+}$      | VBS Supply Under-Voltage, Positive Going Threshold    | 9.4  | 10.2 | 11   | V     |                           |

| $V_{\mathrm{BSUV}}$  | VBS supply Under-Voltage,<br>Negative Going Threshold | 8.4  | 9.2  | 10   | V     |                           |

| $V_{\mathrm{BSUVH}}$ | VBS Supply Under-Voltage Lock- Out<br>Hysteresis      | 0.6  | 1    | -    | V     |                           |

| $I_{QBS}$            | Quiescent VBS Supply Current                          |      | 75   | 120  | uA    | V <sub>IN</sub> =0V or 5V |

| $I_{QCC}$            | Quiescent VCC Supply Current                          |      | 160  | 300  | uA    | V <sub>IN</sub> =0V or 5V |

| $I_{IN+}$            | Input Bias Current                                    |      | 25   | 50   | uA    | V <sub>IN</sub> =5V       |

| I <sub>IN-</sub>     | Input Bias Current                                    |      |      | 1    | uA    | V <sub>IN</sub> =0V       |

| $T_{\mathrm{ON}}$    | Input to Output Propagation Turn-On Delay Time        |      | 500  | 800  | nS    |                           |

| $T_{ m OFF}$         | Input to Output Propagation Turn-Off Delay Time       |      | 200  | 400  | nS    |                           |

| T <sub>FIL,IN</sub>  | Input Filter Time (HIN, LIN)                          |      | 100  |      | nS    |                           |

## **MOSFET Avalanche Characteristics**

| Symbol   | Description                   | Min | Тур | Max | Units | Conditions                        |

|----------|-------------------------------|-----|-----|-----|-------|-----------------------------------|

|          |                               |     |     |     |       | T <sub>J</sub> =25°C, L=36mH,     |

| $E_{AS}$ | Single Pulse Avalanche Energy |     | 157 |     | mJ    | I <sub>AS</sub> =3A, TO-252       |

|          |                               |     |     |     |       | package.                          |

| trr      | Reverse Recovery Time         |     | 85  |     | ns    | I <sub>S</sub> =3A, di/dt=100A/us |

## **Input-Output Logic Level Table**

| HIN  | LIN  | VS   |

|------|------|------|

| High | Low  | HV   |

| Low  | High | PGND |

| Low  | Low  | *    |

| High | High | **   |

<sup>\*</sup> The VS voltage has two states. If the current flows from PGND to VS, the VS voltage is PGND; if the current flows from VS to HV, the VS voltage is HV

REV\_Preliminary\_0.4 5 www.fortiortech.com

<sup>\*\*</sup> Cross-conduction condition

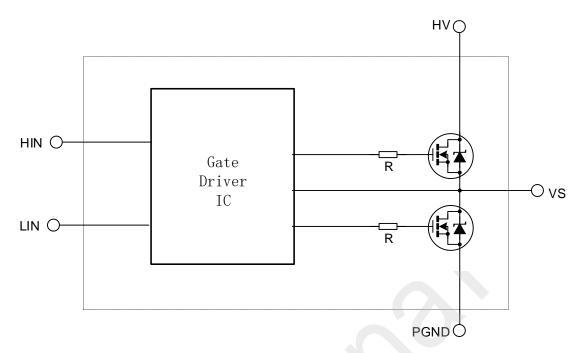

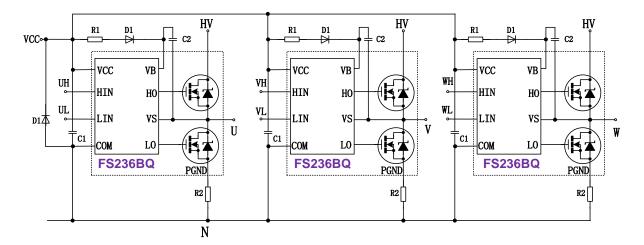

#### **Typical Application**

Figure: Typical Application Connection

- 1. In order to provide a good decoupling between VCC-COM and VB-VS terminals, the capacitors shown in the figure should be connected at these terminals and located very close to the module pins.

- 2. Value of the boot-strap capacitors depends upon the switching frequency.

- 3. Ground wires and output terminals, should be thick and short in order to avoid surge voltage and malfunction of HVIC.

- 4. It is recommended to connect high frequency non-inductive capacitor beside filter capacitor between HV&N with short wire to avoid surge destruction.

- 5. RC filtering capacitor maybe connected to inputs to prevent surge noise caused by wrong input signal.

- 6. High voltage (600V or more) and fast recovery type (less than 100ns) diodes D1 should be used in the bootstrap circuit. A resistor R1 (larger than 100hm) must be added in series with the bootstrap diode.

- 7. To prevent ICs from surge destruction, it is recommended to insert a Zener diode D2 (18V,1W) nearby each pair of supply terminals.

REV\_Preliminary\_0.4 6 www.fortiortech.com

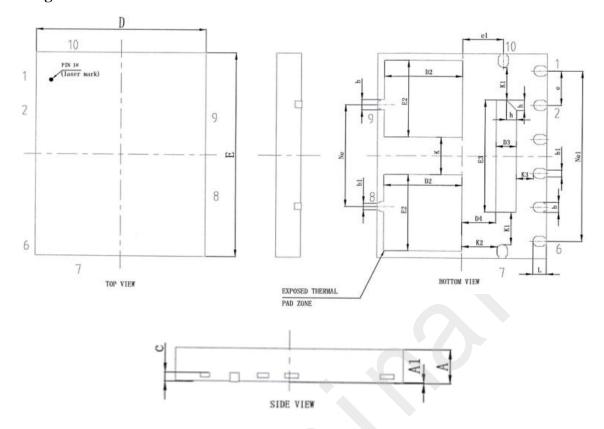

## **Package Outline**

| CVMDOI |         | MILLIMETER |      |

|--------|---------|------------|------|

| SYMBOL | MIN     | NOM        | MAX  |

| A      | 0.70    | 0.75       | 0.80 |

| A1     | 0       | 0.02       | 0.05 |

| b      | 0.25    | 0.30       | 0.35 |

| b1     |         | 0.21REF    |      |

| С      |         | 0.203REF   |      |

| D      | 4.90    | 5.00       | 5.10 |

| D2     | 2.20    | 2.30       | 2.40 |

| D3     | 0.50    | 0.60       | 0.70 |

| D4     | 0.95    | 1.00       | 1.05 |

| e      |         | 1.00BSC    |      |

| e1     |         | 1.20BSC    |      |

| Ne     |         | 3.00BSC    |      |

| Ne1    |         | 5.00BSC    |      |

| Е      | 5.90    | 6.00       | 6.10 |

| E2     | 2.15    | 2.25       | 2.35 |

| E3     | 3.20    | 3.30       | 3.40 |

| L      | 0.35    | 0.40       | 0.45 |

| h      | 0.25    | 0.30       | 0.35 |

| K      | 1.10REF |            |      |

| K1     | 0.95REF |            |      |

REV\_Preliminary\_0.4 7 www.fortiortech.com

| K2 | 1.05REF |

|----|---------|

| K3 | 0.50REF |

| Part Number | Package Type | Marking ID | Package Method | Quantity |

|-------------|--------------|------------|----------------|----------|

| FS236BQ     | QFN10L-5*6   | FS236BQ    | Tray           | 490      |

REV\_Preliminary\_0.4 8 www.fortiortech.com

## **Copyright Notice**

Copyright by Fortior Technology (Shenzhen) Co., Ltd. All Rights Reserved.

Right to make changes —Fortior Technology (Shenzhen) Co., Ltd reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. The information contained in this manual is provided for the general use by our customers. Our customers should be aware that the personal computer field is the subject of many patents. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. It is the policy of Fortior Technology (Shenzhen) Co., Ltd. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

This manual is copyrighted by Fortior Technology (Shenzhen) Co., Ltd. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the expressly written permission from Fortior Technology (Shenzhen) Co., Ltd.

## Fortior Technology (Shenzhen) Co., Ltd.

Room203, 2/F, Building No.11, Keji Central Road2,

Software Park, High-Tech Industrial Park, Shenzhen, P.R. China 518057

Tel: 0755-26867710 Fax: 0755-26867715

URL: http://www.fortiortech.com

#### Contained herein

Copyright by Fortior Technology (Shenzhen) Co., Ltd, all rights reserved.

REV\_Preliminary\_0.4 9 www.fortiortech.com